# Electrical Characterization of N-MOS and P-MOS Junctionless Gate-All-Around (GAA) Mosfet for an Inverter Application

Ho Kok Pow<sup>1</sup>, Mathan N<sup>2</sup>, Mohamed Sultan Mohamed Ali<sup>1</sup>, Muhammad Luqman Mohd Napi<sup>1</sup>, Ali Hosseingholipouras<sup>1</sup>, and Fatimah Khairiah Abd Hamid<sup>1\*</sup>

<sup>1</sup>School of Electrical Engineering, Universiti Teknologi Malaysia, 81310 UTM Skudai, Johor, Malaysia.

<sup>2</sup>Department of Electronics and Communication Engineering, Sathyabama Institute of Science and Technology, Chennai, India

Corresponding author: fatimahkhairiah@gmail.com, Tel: 011-23509474

Abstract: This paper presents a numerical simulation to examine the electrical performance of a Junctionless Gate-All-Around (JGAA) Field Effect Transistor (FET) as an inverter. The advantages of the device offer smaller threshold voltage, lower leakage current, better electrostatic control, better device performance and can operate at a high speed. Thus, to examine the potential of the device for an inverter application, the characterization of the Junctionless GAA MOSFET is performed to identify the critical device parameters in optimizing the device performance. Besides, the optimization of the device is aimed to be used to meet IRDS standard, particularly for a low power application. The characterization of electrical properties conducted based on carrier concentration, radius, gate length and drain voltage. It is found that the drain voltage and gate length give a significant impact on the threshold voltage and on-state current of the Junctionless GAA MOSFET but the minimum impact on its leakage current. However, the device parameters such as carrier concentration and radius of the channel contributed significant impact on the threshold voltage, on-state current and leakage current. The simulated result of the optimized device for N-MOS and P-MOS indicates that its electrical properties enhanced significantly. For N-MOS, the threshold voltage, current-ratio and subthreshold and drain induced barrier lowering were calculated as 0.350V, 1.606, 60 mV and 40.04 mV/dec, respectively, meanwhile for P-MOS, the threshold voltage, current-ratio and subthreshold and drain induced barrier lowering were obtained as 0.355V, 4.132, 60 mV and 60.6 mV/dec, accordingly. These results revealed that the Junctionless GAA MOSFET could meet the requirement set by IRDS for a low power application which can offer minimum leakage current and suitable to be used for an inverter application.

Keywords: Junctionless GAA MOSFET, Inverter.

Article History: received 25 May 2021; accepted 12 June 2021; published 15 September 2021.

© 2021 Penerbit UTM Press. All rights reserved

## 1. INTRODUCTION

Technology roadmaps become the pillar of the semiconductor industry for many years. The first roadmap was Moore's law, which started as an empirical observation that competitive forces then turned into a prediction that became an industry roadmap. Then, the International technology roadmap semiconductor (ITRS) roadmap was developed and used by leading-edge semiconductor producers to drive the new technology needed. The recent roadmap is known as the International Roadmap Device Semiconductor (IRDS) roadmap, which provides the guideline in semiconductor end-user requirements and develops a technology roadmap based on those requirements [1]. The International Roadmap for Devices and Semiconductors (IRDS) provides a guideline to simplify research coordination, manufacturing supply and academic relating to the development and

implementation of electronic systems and devices. In the

past, simple shrinks of critical dimensions for CMOS logic devices offer an improvement in their performance. Advancements in patterning technology directly gave improved devices. However, as device dimensions got smaller and smaller, electrical factors such as current leakage forced innovation in device design based on material or architecture [2-5]. In 2011, the Fin-FET was introduced to manufacturing, where the gate was redesigned into a vertical structure to improve leakage performance and give better performance. Fin-FETs are expected to be replaced by Lateral Gate-All-Around structures (LGAA), then by Vertical Gate-All-Around structures (VGAA), which will then scale in 3D instead of shrinking further. Junctionless Field Effect Transistor is introduced in IRDS as an alternative device that can be implemented for a low power application.

Junctionless GAA MOSFETs are introduced to overcome the uncontrollable leakage current in conventional GAA MOSFET which susceptible to the changes in the radius of the channel. For a Junctionless

GAA, the main prerequisite of the device is the source, drain and channel region must be heavily doped. The advantages of the Junctionless GAA offers a lower leakage current and smaller threshold voltage which causes the devices operates faster at higher performances. Besides, the fabrication process also much simpler compared to the conventional structures. Most of the existing works related to the Junctionless GAA MOSFETs reported on the analysis related to their physical and electrical characteristic [4-7]. Moreover, there are fewer findings emphasized on the crucial device parameter that assisting in the optimization and application as an inverter. Thus, in this work, the characterization of the Junctionless GAA MOSFET is performed to identify the critical device parameters in optimizing the device performance. The characterized device is further continued for an inverter application and their electrical performance are compared with IRDS standard and other published works for a low power application.

## 2. METHODOLOGY

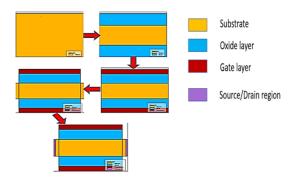

A Junctionless GAA MOSFET is built by using TCAD tools as shown in Figure 1[8]. Firstly, all the device parameters should be decided. Then, the idea is executed by designing the proposed device using the TCAD tool. To achieve a smaller leakage current, the thickness of the channel is recommended to be narrow and thin to allow the device to operate in depletion modes. The most important consideration in designing Junctionless MOSFET is the doping level for source, drain and channel must be heavily doped with uniform concentration to ensure the device operated under accumulation mode for both n-type or ptype. The process used to develop a Junctionless GAA MOSFET started by constructing the substrate layer followed by depositing the oxide layer and gate layer where polysilicon material is used as a gate material. Then, the source, drain, gate and channel regions are assigned accordingly before performing the electrical characterization.

Table 1. Device parameter used for N-MOS and PMOS

| Device                          | N-MOS                | P-MOS                |  |

|---------------------------------|----------------------|----------------------|--|

| parameters                      |                      |                      |  |

| Doping (cm <sup>-3</sup> )      | 1.5x10 <sup>19</sup> | $1.0x10^{19}$        |  |

| Length of source and drain (nm) | 5.10                 | 5.10                 |  |

| Gate length (nm)                | 1000                 | 1000                 |  |

| Oxide thickness (nm)            | 6.00                 | 6.00                 |  |

| Radius (nm)                     | 2.50                 | 5.00                 |  |

| $V_{DS}(V)$                     | 0.01                 | 0.01                 |  |

| Gate thickness (nm)             | 3.00                 | 3.00                 |  |

| Mobility $(cm^2/Vs)$            | 90                   | 45                   |  |

| Doping cm <sup>-3</sup>         | 1.5x10 <sup>19</sup> | 1.0x10 <sup>19</sup> |  |

Figure 1. Process to build the Junctionless GAA MOSFET.

# 3. RESUTLS AND DISCUSSION

In this section, validation of the device parameters is performed by comparing its electrical behaviour with published data meanwhile characterization of the developed device will be further discussed based on drain voltage, radius, gate length and doping concentration.

## 3.1 Validation

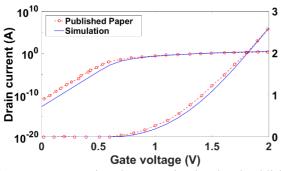

Table 1 shows the device parameters used to characterize the device performance of the Junctionless Gate- All-Around MOSFET. Meanwhile, Table 2 indicates the device parameters used to validate the device parameter used in this work with published data. From Figure 2, it should be noticed that the value of device parameters used is in lined with published work where the discrepancy is estimated as less than 5%. Thus, the device parameters used in this work in the acceptable range.

Table 2. Validation of developed device with published data.

| Device              | Our work Published dat |                         |  |  |

|---------------------|------------------------|-------------------------|--|--|

| parameters          |                        | [9]                     |  |  |

| Doping $(cm^{-3})$  | $2.5 \times 10^{18}$   | $5x10^{18}$ $1x10^{19}$ |  |  |

| Work function       | 4.67                   | -                       |  |  |

| (V)                 |                        |                         |  |  |

| Length of           | 5.10                   | =                       |  |  |

| source & drain      |                        |                         |  |  |

| (nm)                |                        |                         |  |  |

| Gate length         | 1000                   | 1000                    |  |  |

| (nm)                |                        |                         |  |  |

| Oxide thickness     | 6.00                   | 5.00                    |  |  |

| (nm)                |                        |                         |  |  |

| Radius (nm)         | 5.00                   | 5.00                    |  |  |

| V <sub>DS</sub> (V) | 1.00                   | 1.00                    |  |  |

| Gate thickness      | 3.00                   | -                       |  |  |

| (nm)                |                        |                         |  |  |

| Mobility            | 90                     | 100                     |  |  |

| $(cm^2/Vs)$         |                        |                         |  |  |

Figure 2. A comparison between simulated and published

# 3.2 Variation of drain current versus gate voltage ( $I_{ds}$ - $V_{gs}$ ) graph analysis

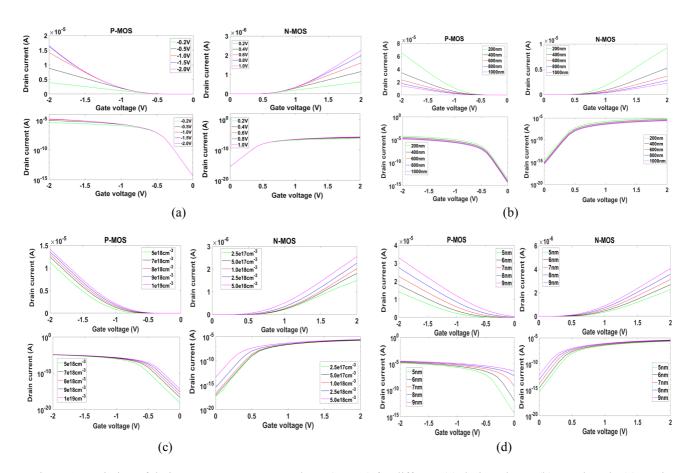

Figure 3 depicts the variation of drain current against the gate voltage for various drain voltages, gate lengths, channel radii, and carrier concentrations. In general, the variation of those parameters can give a direct impact on its electrical properties as indicated by the changes in the  $I_{\rm ds}\text{-}V_{\rm gs}$  for both P-MOS and N-MOS. The drain voltage and gate length give a significant effect on the threshold and on-state current as shown in Figure 3(a-b) but less impact on its leakage current. However, the device parameters such as carrier concentration and radius of the channel contributed to the changes of the threshold voltage, on-state current and leakage current as seen in Figure 3(c-d).

From these results, the changes of the radius and carrier concentration are the critical parameters need to be considered when optimizing the device performance. The changes of simulated results based on drain voltages, gate length, radius, and doping is aligned with reported data in [10-11].

## 3.3 Device Optimization and benchmarking.

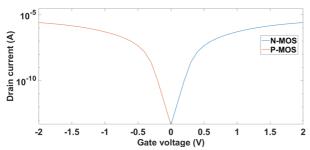

Figure 4 shows the  $I_{ds}\mbox{-}V_{gs}$  for P-MOS and N-MOS Junctionless GAA MOSFET. The electrical parameters of the device were extracted and tabulated in Table 3. According to the latest IRDS prediction (2018), the targeted threshold voltage, current ratio and subthreshold swing for low power or high-density application are reported as 363 mV, 1.271x10' and 75mV/dec respectively. For DIBL, the targeted value is less than 100 mV/V. In overall, the behaviour of the developed device exhibited much better electrical performance in comparison to other published work in term of its threshold voltage, current ratio and subthreshold swing. Despite higher the drain induced barrier lowering, the values are still considered in the ideal range. Thus, the electrical performance of the developed device summarized in Table 2 indicates that the developed device is suitable to be used for a low power application since the device could offer minimum leakage current [9].

Figure 3. Variation of drain current versus gate voltage ( $I_{ds}$ - $V_{gs}$ ) for different (a) drain voltage, (b) gate length, (c) carrier concentration and (d) radius of the channel.

Figure 4. The drain current versus gate voltage for P-MOS and N-MOS Junctionless GAA MOSFETs.

Table 3. Validation of developed device with published data.

| Device<br>type                                   | V <sub>th</sub> (mV) | $\frac{I_{on}/}{I_{off}(10^7)}$ | SS (mV/dec) | DIBL<br>(mV/V) | refs      |

|--------------------------------------------------|----------------------|---------------------------------|-------------|----------------|-----------|

| Junctionl<br>ess GAA<br>MOSFE<br>T (N-<br>MOS)   | 350                  | 1.606                           | 60          | 40.404         | This work |

| Junctionl<br>ess GAA<br>MOSFE<br>T (P-<br>MOS)   | -355                 | 4.132                           | 60          | 60.606         | This work |

| GAA<br>MOSFE<br>T                                | 394                  | 0.1                             | 113.89      | -              | [12]      |

| Junctionl<br>ess GAA<br>MOSFE<br>T               | -                    | 0.0714                          | 73          | 13             | [13]      |

| Junctionl<br>ess<br>Double<br>Gate<br>MOSFE<br>T | 350                  | _                               | 110         | 65             | [14]      |

## 4. CONCLUSION

In this work, a Junctionless GAA MOSFET structure is created and its electrical characteristics were simulated using the TCAD tool. The Junctionless type of GAA MOSFET is achieved by applying homogenous doping at the source, drain and channel regions and the doping must be heavily doped. The drain voltage and gate length have a significant impact on the threshold voltage and on-state current of the Junctionless GAA MOSFET but less impact on its leakage current. Nevertheless, the device parameters such as carrier concentration and radius of the channel contributed to the changes of the threshold voltage, onstate current and leakage current. The electrical performance of the optimized device revealed that the Junctionless GAA MOSFET can meet the requirement set by IRDS for a low power application that can offer minimum leakage current. The junctionless device also can be implemented as a basic circuit like an inverter and therefore could be used for a complex application such as a memory application that needs high performance with minimum leakage current.

## **ACKNOWLEDGMENT**

The authors would like to acknowledge the support from the Unversiti Teknologi Malaysia for providing an excellent research environment to make this work possible.

## REFERENCES

- [1] M. Neisser (2018). The 2017 IRDS Lithography Roadmap. Journal of Microelectronic Manufacturing, vol. 1, no. 2, pp. 1-8.

- [2] N Mathan, S Jayashri, Nurul Ezaila Alias, Michael Loong Peng Tan, "Performance Analysis of Montgomery Multiplier using 32nm CNTFET Technology", Indonesian Journal of Electrical Engineering and Informatics (IJEEI) Vol. 7, No. 4, Dec 2019, pp. 697~702

- [3] Mathan Natarajamoorthy, Jayashri Subbiah, Nurul Ezaila Alias, Michael Loong Peng Tan, "Stability Improvement of an Efficient Graphene Nanoribbon Field-Effect Transistor-Based SRAM Design", Journal of Nanotechnology, vol. 2020, Article ID 7608279, 7 pages, 2020.

- [4] Wang, T., Lou, L., and Lee, C. (2013). A junctionless gate-all-around silicon nanowire FET of high linearity and its potential applications. IEEE Electron Device Letters, 34(4), 478-480.

- [5] Lime, F., Moldovan, O., and Iñiguez, B. (2014). A compact explicit model for long-channel gate-allaround junctionless MOSFETs. Part I: DC characteristics. IEEE Transactions on Electron Devices, 61(9), 3036-3041.

- [6] Bendib, T., Djeffal, F., and Meguellati, M. (2014). An optimized junctionless GAA MOSFET design based on multi-objective computation for high-performance ultra-low power devices. Journal of Semiconductors, 35(7), 074002.

- [7] Merad, F., and Guen-Bouazza, A. (2020). DC performance analysis of a 20nm gate length n-type silicon GAA junctionless (Si JL-GAA) transistor. International Journal of Electrical and Computer Engineering, 10(4), 4043.

- [8] Silvaco Process and Device Simulation, URL: http://www.silvaco.com

- [9] J. P. Duarte, S.-J. Choi, D.-I. Moon, and Y.-K. Choi (2011). A nonpiecewise model for long-channel junctionless cylindrical nanowire FETs. IEEE Electron Device Letters, vol. 33, no. 2, pp. 155-157.

- [10] Hamid, F. K., Johari, Z., Alias, N. E., Lim, W. H., Sultan, S. M., Leong, W. S., and Ismail, R. (2020). Modeling of inversion and centroid charges of long channel strained-silicon surrounding gate MOSFETs incorporating quantum effects. Semiconductor Science and Technology, 35(2), 025010.

- [11] Rahman, I. R., Khan, M. I., and Khosru, Q. D. (2021). Analytical drain current and performance evaluation for inversion type InGaAs gate all-around MOSFET. AIP Advances, 11(6), 065108.

- [12] S. Z. Reza, M. S. Islam, and F. Al Mamun (2017). A Comparative Study of Electrical Properties of Si and ZnO Gate-all-around Nanowire FET. International Journal of Engineering Inventions, pp. 58-66

- [13] M. Rony, P. Bhowmik, H. R. Myler, and P. Mondol 2016. Short Channel Effects suppression in a dualgate Gate-All-Around Si nanowire junctionless

- nMOSFET. in 2016 9th International Conference on Electrical and Computer Engineering (ICECE), pp. 538-541.

- [14] C. Jiang, R. Liang, J. Wang, and J. Xu (2015). A twodimensional analytical model for short channel junctionless double-gate MOSFETs. *AIP Advances*, vol. 5, no. 5, p. 057122.