# Sequential Capacitor Placements Method for Voltage Improvement in Transmission Networks

## Mohammad Azalie Asrof Romzi and Jasrul Jamani Jamian\*

Faculty of Electrical Engineering, Universiti Teknologi Malaysia, 81310 UTM Skudai, Johor, Malaysia.

\*Corresponding author: jasrul@fke.utm.my, Tel: 607-5557227

**Abstract:** The voltage profile in a transmission line system should be in the tolerance of the lower limit to the upper limit value. Moreover, the power loss during transmission process should be minimized to increase the lifespan of the transmission lines. The poor voltage profile and high power losses are the results of increasing of power demand due to the arising of electrical energy consumptions. These problems can be solved by using the shunt capacitor bank placements. The installation of capacitors required three specifications which are the locations, size and number of capacitors to improve the voltage profile of overall system. However, these three specifications are difficult to be determined. The best locations for capacitor placements will result in minimum number and size. In this study, the specifications of capacitor is based on voltage increment algorithms. The proposed methods will be applied on three transmission networks which are 6-bus system, 14-bus system and 30-bus system using Power World Simulator. The results show that the proposed method able to improve the overall voltage profile and reducing the power loss with minimum number of capacitor placement in the transmission networks.

Keywords: Power loss reduction, shunt capacitor bank placements, transmission networks, voltage profile improvement.

#### **1. INTRODUCTION**

In this new era of globalization, the demand for power is growing larger as the consumption of electrical energy is increasing. However, the increased in demand will cause more stress on the transmission systems and this phenomenon can lead to poor voltage profile of the networks. Sufficient reactive power is very important to maintain the voltage profile in a proper range [1]. Besides, the high power loss will reflect the shorter life span and less reliable of the transmission network. Thus, it is important to improve the voltage profile and reduce the power loss of the transmission network to increase the reliability. Several units of shunt capacitor bank can be used to improve voltage profile, minimize feeder demand and reduce power loss [2].

As the main cause of poor voltage profile is due to the insufficient reactive power delivered, the improvement of voltage profile can be achieved by installing shunt capacitor banks. Many methods have been proposed regarding the improvement of voltage profile using capacitor placements. The simplest approaches is introduced in [3]. The capacitor bank is placed at the bus with lowest voltage profile and the authors have found the placement will greatly improve the voltage profile. Aside from using this approach, a simple computer programming for locating shunt capacitors on primary feeder for voltage control and loss reduction is proposed in [4]. In their research, the authors had identified the suitable sizes for capacitor banks based on the amount of voltage to be increased through the computational © 2017 Penerbit UTM Press. All rights reserved

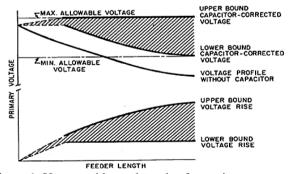

programming. The different size of capacitor bank will give different level of voltage increment. The available capacitor sizes and the amount of voltage to be corrected of each size of capacitors are determined as shown in Figure 1.

Figure 1. Upper and lower bounds of capacitor-corrected voltage and capacitor voltage rise

In line with this work, authors in [5] used Equation (1) to determine the percentage voltage increment due to compensation of MVAr size of capacitor. The determination of the voltage increment is involving the distance of the capacitor bank from the source. The greatest voltage rise can be achieved at the installation location of the shunt capacitor bank.

%Voltage rise =

$$\frac{(kVAr)(d)(X)}{(10)(kV)^2}$$

(1)

Where,

| % Voltage rise | : | The percentage of voltage increment                                               |

|----------------|---|-----------------------------------------------------------------------------------|

| kVAr           | : | Power rating of the shunt capacitor                                               |

| d              | : | Distance of capacitor installation                                                |

| Х              | : | location from the source in km<br>Reactance of the line in ohm per unit<br>length |

| kV             | : | Line-to-line voltage in kV                                                        |

Not only limited to mathematical formulation, the capacitor banks placement can also being identified using Meta-heuristic technique. A few Meta-heuristic algorithms are used in the in this study, such as Crow Search Algorithm (CSA) [6], Genetic Algorithm (GA) [7]-[9] and Particle Swarm Optimization (PSO) [10]-[12]. Although these algorithms able to provide simultaneous capacitor banks placement results, however, its required several trials in order to ensure result is valid. Indirectly, it will consume a lot of time. Furthermore, the algorithm required some knowledge on possibility search space. Without all these information, the technique will not able to provide better result.

Therefore, in this paper, the sequential capacitor banks placement and sizing based on power loss and adjacent voltage improvement are proposed. The algorithm will be tested on 3 different transmission systems.

#### 2. METHODOLOGY

#### 2.1 Simulation of the Transmission Networks

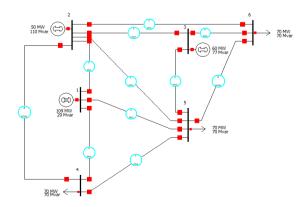

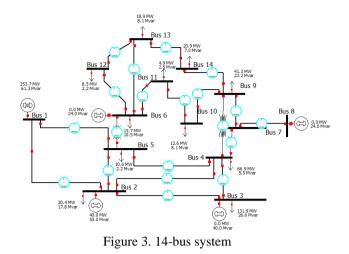

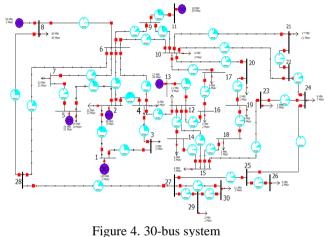

Figures 2, 3 and 4 show the 6-Bus system, 14-Bus system and 30-Bus system transmission networks used for this study respectively. The system data such as bus data, line data and transformer data are taken from IEEE standards data. The original networks of these transmission systems have voltage profile within 0.95 per unit to 1.10 per unit. In order to test the proposed sequential capacitor placement method, the loads in all these systems are increased by certain percentages.

As a result, the overall loads are increased by 50%, 75% and 100% for 6-bus and 30-bus systems. Meanwhile, the overall loads are increased to 175% and 200% for the 14-bus system. With this condition, there will have some buses in the system that operated below then 0.95 p.u. In this study, the MVA limits of the transmission lines for all the systems is assumed to very large to overcome the overload due to the increasing of the loads.

Figure 2. 6-bus system

Figure 4. 30-bus system

#### 2.2 Capacitor Placements Method

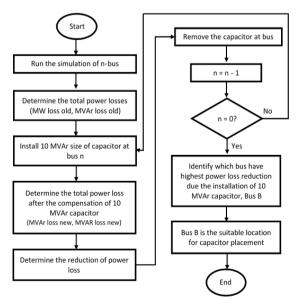

The suitable location of capacitor placement will give minimum size of capacitor in order to improve the voltage profile at all buses. In order to find the suitable location for capacitor placement, sequential capacitor placements method based on total power loss reduction after capacitor installation is used in this study. The process of this method is shown by using the flowchart in Figure 5.

Figure 5. Flowchart for identifying the location for capacitor placement

The location for the installation of capacitor is identified based on observation on the power loss reductions by individual bus due to compensation of 10 MVAr size of capacitor. The power losses reduction are calculated by using Equation (2) and Equation (3).

| $\sum_{i=1}^{n} MW \text{ loss reduction} = \sum_{i=1}^{n} MW \text{ loss old} - \sum_{i=1}^{n} MW \text{ loss new}$       | (2) |

|----------------------------------------------------------------------------------------------------------------------------|-----|

| $\sum_{i=1}^{n} MVAr \text{ loss reduction} = \sum_{i=1}^{n} MVAr \text{ loss old} - \sum_{i=1}^{n} MVAr \text{ loss new}$ | (3) |

| where,                                                                                                                     |     |

| MXX 1 a a a da ati a a |   | A adiena a access 1 a an an decadio a |

|------------------------|---|---------------------------------------|

| MW loss reduction      | : | Active power loss reduction           |

|                        |   | after compensation of shunt           |

|                        |   | capacitor bank                        |

| MW loss old            | : | Active power loss of the bus          |

|                        |   | before compensation of                |

|                        |   | shunt capacitor bank                  |

| MW loss new            | : | Active power loss of the bus          |

|                        |   | after compensation of shunt           |

|                        |   | capacitor bank                        |

| MVAr loss reduction    | : | Reactive power loss                   |

|                        |   | reduction after compensation          |

|                        |   | of shunt capacitor bank               |

| MVAr loss old          | : | Reactive power loss                   |

|                        |   | reduction before                      |

|                        |   | compensation of shunt                 |

|                        |   | capacitor bank                        |

| MVAr new               | : | Reactive power loss                   |

|                        |   | reduction after compensation          |

|                        |   | of shunt capacitor bank               |

| n                      | : | number of bus of the system           |

|                        | • |                                       |

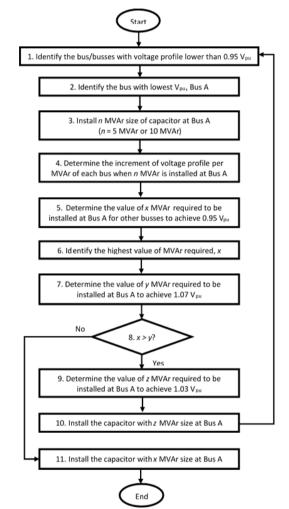

## 2.3 Determining Sizes and Number of Capacitors

There are eleven simple steps to get suitable size and number of capacitor required in any system as shown in Figure 6. This method is based on the increment of voltage due the installation of capacitor at the bus with lowest voltage profile. The increment of voltage profile per MVAr in step 4 is calculated by using Equation (4).

$$V_{pu} \text{ per } MVAr = \frac{V_{pu \text{ new}} - V_{pu \text{ old}}}{n}$$

(4)

where,

| V <sub>pu</sub> per MVAr | : | Increment of per unit voltage per 1 |

|--------------------------|---|-------------------------------------|

|                          |   | MVAr capacitor                      |

| V <sub>pu new</sub>      | : | Per unit voltage profile after the  |

| 1                        |   | compensation of n MVAr size of      |

|                          |   | capacitor at the bus with lowest    |

|                          |   | voltage profile                     |

| $V_{pu \ old}$           | : | Per unit voltage profile before the |

| 1                        |   | compensation of n MVAr size of      |

|                          |   | capacitor at the bus with lowest    |

|                          |   | voltage profile                     |

| n                        | : | MVAr size of capacitor installed at |

|                          |   | the bus with lowest voltage profile |

The value of MVAr required for x, y and z, which are in steps 5, 7 and 9, are calculated by using Equation (5).

$$MVAr_{required} = \frac{V_{pu \ desired} - V_{pu \ old}}{V_{pu} \ per \ MVAr}$$

(5)

Where,

| : | MVAr size of capacitor required for    |

|---|----------------------------------------|

|   | the bus to achieved desired per unit   |

|   | voltage                                |

| : | Per unit voltage desired.              |

|   | For x, $V_{pu \text{ desired}} = 0.95$ |

|   | For y, $V_{pu \text{ desired}} = 1.07$ |

|   | For z, $V_{pu \text{ desired}} = 1.03$ |

| : | Per unit voltage of individual bus     |

|   | before the compensation of n MVAr      |

|   | size of capacitor at the bus with      |

|   | lowest voltage profile                 |

|   |                                        |

Figure 6. Flowchart for determining the size and number of capacitors for capacitor placement

## 3. RESULT AND DISCUSSION

#### 3.1 First Locations for Capacitor Placements

Tables 1 and 2 show the results of identifying the location for the capacitor placements based on maximum power loss reduction. Both results are obtained from two case studies, which are:

- a) 6-bus system with 150% loads

- b) 6-bus system with 175% loads

The analysis of these two cases follows the process as described in the flowchart in Figure 5. Firstly, the overall loads of the 6-bus system are increased by 50 percent and

the corresponding reactive and active power losses are determined. Then, a 10 MVAr capacitor is installed at Bus 6. The power loss due to the installation of the capacitor is determined and the reduction in power loss is calculated. Next, the capacitor is removed from Bus 6 and installed at Bus 5. The same analysis on the power loss is done and the flow is repeated until the last location which is at Bus 1. For the second case, the loads are increased by 75 percent and the overall process as in the first case is repeated.

| Table 1. 6-bus system with 150% loads | Table 1. | 6-bus | system | with | 150% | loads |

|---------------------------------------|----------|-------|--------|------|------|-------|

|---------------------------------------|----------|-------|--------|------|------|-------|

|                                                    |   | Powe  | er Loss |      | er Loss<br>uction |

|----------------------------------------------------|---|-------|---------|------|-------------------|

|                                                    |   | MW    | MVAr    | MW   | MVAr              |

|                                                    |   | loss  | loss    | loss | loss              |

| Before<br>Compensation                             |   | 27.61 | 57.82   |      |                   |

|                                                    | 1 | 27.61 | 57.82   | 0    | 0                 |

| After                                              | 2 | 27.61 | 57.82   | 0    | 0                 |

| Compensation<br>of 10 MVAr<br>Capacitor at<br>Bus: | 3 | 27.61 | 57.82   | 0    | 0                 |

|                                                    | 4 | 26.78 | 55.74   | 0.83 | 2.08              |

|                                                    | 5 | 26.75 | 55.16   | 0.86 | 2.66              |

|                                                    | 6 | 27.12 | 55.88   | 0.49 | 1.94              |

Table 2. 6-bus system with 175% loads

|                                                             |   | Power Loss |        | Power Loss<br>Reduction |      |

|-------------------------------------------------------------|---|------------|--------|-------------------------|------|

|                                                             |   | MW         | MVAr   | MW                      | MVAr |

|                                                             |   | loss       | loss   | loss                    | loss |

| Before<br>Compensation                                      |   | 44.18      | 107.00 |                         |      |

|                                                             | 1 | 44.18      | 107.00 | 0                       | 0    |

| After<br>Compensation<br>of 10 MVAr<br>Capacitor at<br>Bus: | 2 | 44.18      | 107.00 | 0                       | 0    |

|                                                             | 3 | 44.18      | 107.00 | 0                       | 0    |

|                                                             | 4 | 43.06      | 104.24 | 1.12                    | 2.76 |

|                                                             | 5 | 42.97      | 103.46 | 1.21                    | 3.54 |

|                                                             | 6 | 43.51      | 104.53 | 0.67                    | 2.47 |

In the first case (load increase by 50%), power loss reduction is achieved by the installation of 10 MVAr capacitor in the network. The greatest power loss reduction is achieved when the capacitor placed at Bus 5. The same pattern of results is also shown by second case (175%). Bus 5 is the most suitable location for achieving the high power loss reduction, even with additional of 75% load. Therefore, it can be concluded that the suitable location for capacitor placement is at Bus 5 for 6 bus system.

The process is repeated for IEEE 14 bus and 30 bus systems. In 14 bus system, there are five buses with voltage profile less than 0.95 per unit and lowest voltage profile is at Bus 14. Thus, when the load is increased up to 300%, the best capacitor placement is at bus 14. For IEEE 30 bus system with 200% of load, the suitable location for the capacitor bank is at bus 30. However, unlike 6 bus system, 1 capacitor is not enough to improve the voltage profile in these 2 systems. Therefore, the process to identify minimum number of capacitor will be discussed in next chapter.

## 3.2 Determining the Size and Number of Capacitors

In this section, the method to determine the number and size of capacitors will be discussed. The analysis is done based on three different cases as listed.

Case 1: 6-bus system with 150% loads

- Case 2: 14-bus system with 300% loads

- Case 3: 30-bus system with 200% loads

## 3.2.1 Case 1: 6-bus system with 150% loads

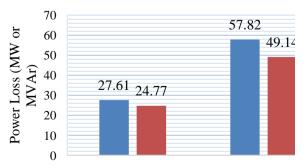

As discussed in Section 3.1, the suitable location for this system is at Bus 5. By using proposed algorithm in (4) and (5), one capacitor is enough to improve the voltage profile of the system up to 0.95 p.u. The optimum value of the capacitor is 35.1 MVAr as shown in Table 3. From Figure 7, the power loss is reduced for both reactive and active power loss. The reduction in MVAr loss is greater compared to the reduction of MW loss. The active and reactive power loss are reduced by 10.29% and 15.01% respectively.

| Table 3. Voltage profile of 6-bus system with 150% loads |  |

|----------------------------------------------------------|--|

| before and after compensation                            |  |

| Bus | Before<br>Compensation<br>V <sub>pu</sub> | After Compensation<br>of 35.1 MVAr<br>Capacitor at Bus 5<br>V <sub>pu</sub> |

|-----|-------------------------------------------|-----------------------------------------------------------------------------|

| 1   | 1.05000                                   | 1.05000                                                                     |

| 2   | 1.05001                                   | 1.05000                                                                     |

| 3   | 1.07002                                   | 1.07000                                                                     |

| 4   | 0.94779                                   | 0.95165                                                                     |

| 5   | 0.92518                                   | 0.95045                                                                     |

| 6   | 0.96314                                   | 0.96818                                                                     |

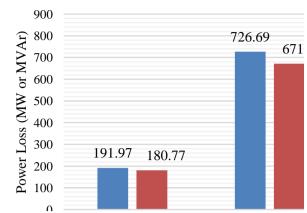

## 3.2.2 Case 2: 14-bus system with 300% loads

One capacitor bank placement is not capable to improve overall voltage profile in 14-bus system. Thus, the analysis of sequential capacitor placement and sizing need to be done. By using same approach, the optimum size of first capacitor is 68 MAVar.

After the installation of the first capacitor, the system will repeat the same process, which is to determine the next suitable capacitor's location. As a result, the next capacitor location is at Bus 4 with the capacity of 120 MVar. The result in Table 5 shows that the voltage of the system is within the tolerance of 0.95 to 1.10 per unit after 2 capacitors placement. The lowest and highest values of voltage after the compensation is 0.95096 and 1.09 per unit at buses 5 and 8 respectively.

Figure 7. Power losses of 6-bus system with 150% loads

Figure 8. Power losses of 14-bus system with 300% loads

Table 5. Voltage profile of 14-bus system with 300% loads before and after compensation

| Bus | Before<br>Compensation | After<br>Compensation<br>of 68.0 MVAr<br>Capacitor at<br>Bus 14 | After<br>Compensation<br>of 120.0<br>MVAr<br>Capacitor at<br>Bus 4 |

|-----|------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------|

|     | V <sub>pu</sub>        | $V_{pu}$                                                        | V <sub>pu</sub>                                                    |

| 1   | 1.06000                | 1.06000                                                         | 1.06000                                                            |

| 2   | 1.04500                | 1.04500                                                         | 1.04500                                                            |

| 3   | 1.01003                | 1.01000                                                         | 1.01000                                                            |

| 4   | 0.90575                | 0.91544                                                         | 0.96840                                                            |

| 5   | 0.90926                | 0.91664                                                         | 0.95096                                                            |

| 6   | 1.07007                | 1.07000                                                         | 1.07000                                                            |

| 7   | 0.96466                | 0.99319                                                         | 1.01942                                                            |

| 8   | 1.09006                | 1.09000                                                         | 1.09000                                                            |

| 9   | 0.91991                | 0.97585                                                         | 1.00287                                                            |

| 10  | 0.92100                | 0.96818                                                         | 0.99096                                                            |

| 11  | 0.98287                | 1.00710                                                         | 1.01883                                                            |

| 12  | 1.01388                | 1.03351                                                         | 1.03599                                                            |

| 13  | 0.98956                | 1.02635                                                         | 1.03121                                                            |

| 14  | 0.88550                | 1.04761                                                         | 1.06825                                                            |

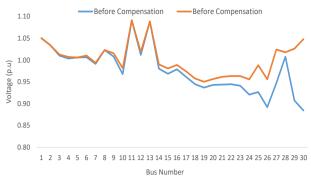

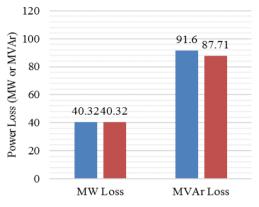

#### 3.3.3 Case 3: 30-bus system with 175% loads

The 30-bus system with 175% load also required two capacitors for improving the overall voltage profile in the network as shown in Figure 9. With the similar process in Section 3.3.2, the placement for capacitors are at Bus 30 and Bus 24 with the size of 21.5 MVAr and 4.7 MVAr respectively. The power loss before and after compensation of capacitors is shown in Figure 10. The active power loss reduction has not significant impact compared to reactive power loss reduction.

From the results, the voltage profile improvement can be achieved by using the proposed method. However, for the reduction of power losses, the active power losses is less affected by the compensation of capacitor. Capacitor placements gave a great impact on the reduction in reactive power loss for all cases.

Figure 9. Voltage Profile of 30-bus system with 175% loads before and after compensation

Figure 10. Power losses of 30-bus system with 175% loads before and after compensation

## 4. CONCLUSION

This paper presents a methodology for capacitor placements and sizing based on sequential approach in order to improve the voltage profile and maximizing the power loss reduction. By using the proposed method, voltage value of each buses are in between 0.95 to 1.10 per unit for all three test bed systems. Furthermore, the minimum number of capacitor required also can be identified. This method could be a great help for the power system planning and operation to overcome the poor voltage profile due to the increased of loads demand.

#### REFERENCES

- Gaikwad, Dattatray N. (2012). Reactive Power Considerations in Reliability Analysis of Solar Photovoltaic Systems. LSU Master's Thesis. Louisiana State University.

- [2] D.M. Tagare (2004). Reactive Power Management. (1st ed.). New Delhi: Tata McGraw-Hill.

- [3] Kyu-Ho Kim and Seok-Ku You. Voltage profile improvement by capacitor placement and control in unbalanced distribution systems using GA.1999 Power Engineering Society Summer Meeting. Conference Proceedings (Cat. No.99CH36364). July 18-22, 1999. Edmonton, Alta. : IEEE. 1999. 800-805.

- [4] N. E. Chang (1969). Transactions on Power Apparatus and Systems. Locating Shunt Capacitors on Primary Feeder for Voltage Control and Loss Reduction. 88(10), 1574-1577.

- [5] H. Wayne Beaty (1998). Electric Power Distribution Systems: A Nontechnical Guide. Tulsa. Oklahoma: PennWell.

- [6] A. Askarzadeh (2016). IET Generation, Transmission & Distribution. Capacitor placement in distribution systems for power loss reduction and voltage improvement: a new methodology. 10(14), 3631-3638.

- [7] N. Kanwar, P. Saini, N. Gupta, A. Swarnkar and K. R. Niazi. Genetic algorithm based method for capacitor placement using new sensitivity based approach. 2014 Eighteenth National Power Systems Conference (NPSC). December 18-20, 2014. Guwahati: IEEE. 2014. 1-6.

- [8] L. S. Vargas and G. A. Jiménez-Estévez. Genetic algorithms for the capacitor placement problem in distribution networks. 2011 16th International Conference on Intelligent System Applications to Power Systems. September 25-28, 2011. Hersonissos: IEEE. 2011. 1-5.

- Kyu-Ho Kim and Seok-Ku You. Voltage profile improvement by capacitor placement and control in unbalanced distribution systems using GA.1999 Power Engineering Society Summer Meeting. Conference Proceedings (Cat. No.99CH36364). July 18-22, 1999. Edmonton, Alta.: IEEE. 1999. 800-805.

- [10] H. Lotfi, M. Samadi and A. Dadpour. Optimal capacitor placement and sizing in radial distribution system using an improved Particle Swarm Optimization algorithm. 2016 21st Conference on Electrical Power Distribution Networks Conference (EPDC). May 5-6, 2016. Karaj: IEEE. 2016. 147-152.

- [11] M. A. A. Razak. Optimal capacitor placement and sizing in an unbalanced three-phase distribution system using particle swarm optimization technique. 2014 International Power 8th Engineering and Optimization Conference (PEOCO2014). March 24-25, 2014. Langkawi: IEEE. 2014. 624-629.

- [12] S. Mandal, K. K. Mandal and B. Tudu. A new hybrid particle swarm optimization technique for optimal capacitor placement in radial distribution systems. 2016 2nd International Conference on Control, Instrumentation, Energy & Communication (CIEC). January 28-30, 2016. Kolkata: IEEE. 2016. 536-540.